# electrónica general

# Lógica Combinacional

Tema 6

### Índice

#### circuitos combinacionales

- 0. Introducción

- 1. Circuitos combinacionales lógicos

- 1.1. Multiplexor

- 1.2. Encoder

- 1.3. Decodificador, Demultiplexor

- 1.4. Convertidores de código

- 2. Circuitos combinacionales aritméticos

- 2.1. Sumador binario

- 2.2. Unidad Lógica Aritmética

### 0. Introducción

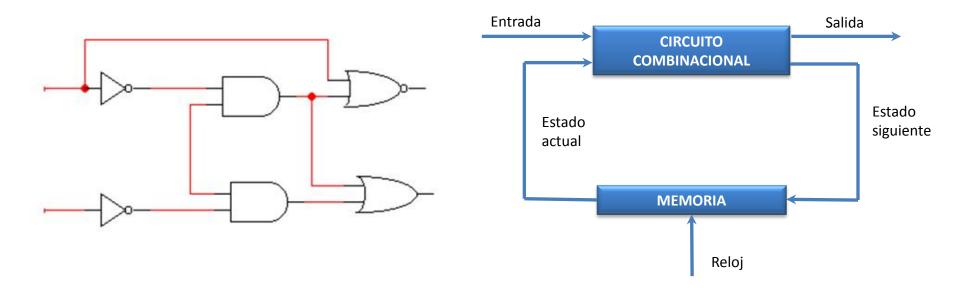

Los circuitos digitales se dividen en dos grupos: los circuitos combinacionales y circuitos secuenciales.

Circuito combinacional: El valor de la salida depende únicamente del valor de las entradas, de tal forma que, para cada combinación de las variables lógicas de entrada, se tiene una salida.

Circuito secuencial: los valores de la salida en un instante dado no solamente depende de los valores de las entradas en ese instante sino también de valores que hayan tenido las entradas en instantes anteriores.

### 0. Introducción

El procedimiento a seguir en el diseño de cualquier circuito combinacional:

- a. Realizar una tabla de verdad de cada una de las salidas del circuito en función de las variables lógicas de entrada.

- **b.** Obtener la función más simplificada posible de cada salida (usando métodos de simplificación que ya hemos visto).

- **c.** Elegir el tipo de puertas y la familia lógica con la que se va a diseñar el circuito combinacional.

#### 1.1. Multiplexor.

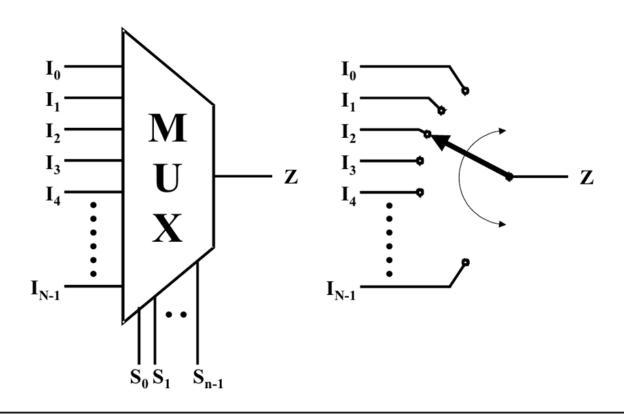

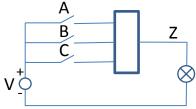

Es un circuito combinacional que realiza la función lógica de seleccionar un dato de entre varios procedentes de distintas fuentes.

Símbolo Lógico de un multiplexor (izquierda) y su similitud con un conmutador mecánico

#### 1.1. Multiplexor.

Para N entradas, se necesitan n entradas de control  $\Rightarrow$  N  $\leq$  2<sup>n</sup>

Utilidad: Compartir una única línea de comunicación por más de un trasmisor

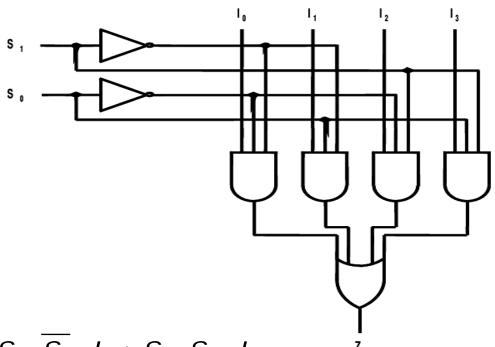

Ejemplo: Multiplexor de 4 entradas

| CON            | SALIDA         |                |

|----------------|----------------|----------------|

| S <sub>1</sub> | S <sub>0</sub> | Z              |

| 0              | 0              | l <sub>o</sub> |

| 0              | 1              | l <sub>1</sub> |

| 1              | 0              | l <sub>2</sub> |

| 1              | 1              | l <sub>3</sub> |

$$Z = \overline{S_1} \cdot \overline{S_0} \cdot I_0 + \overline{S_1} \cdot S_0 \cdot I_1 + S_1 \cdot \overline{S_0} \cdot I_2 + S_1 \cdot S_0 \cdot I_3$$

#### 1.1. Multiplexor.

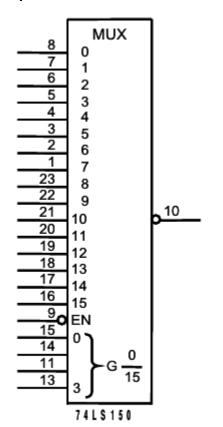

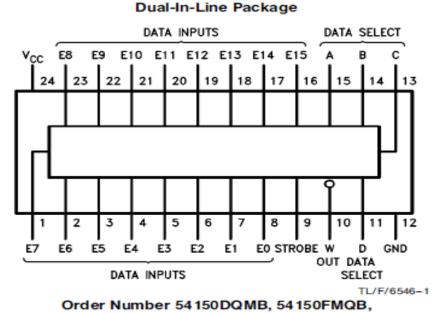

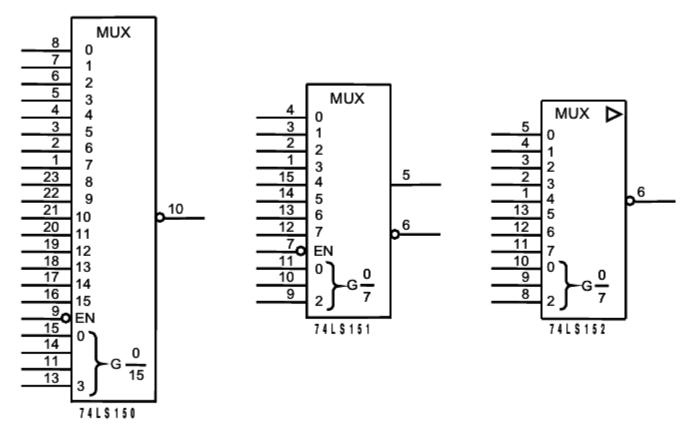

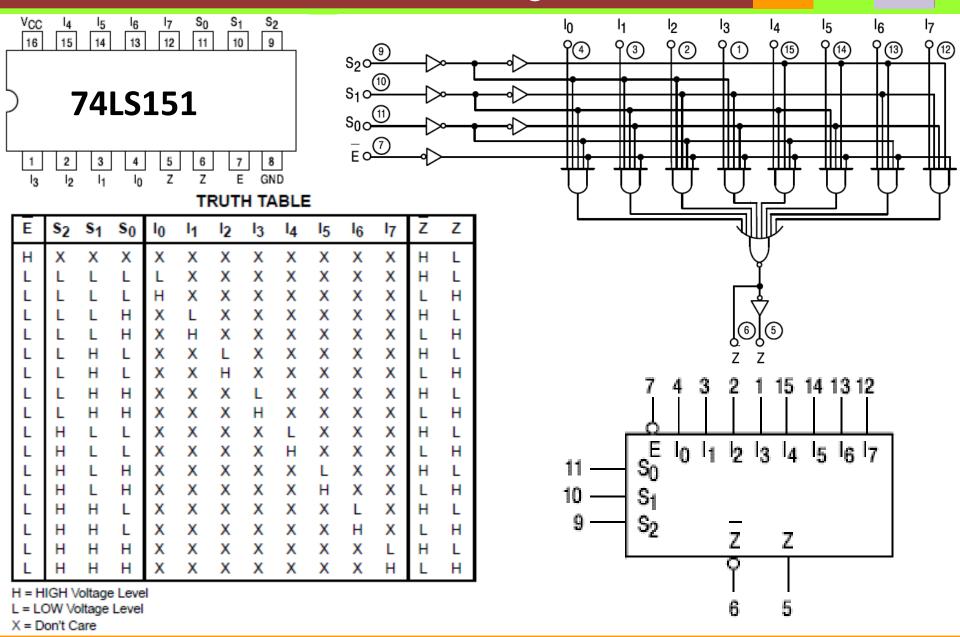

Existen diversos circuitos integrados multiplexores cuyas diferencias estriban, básicamente, en el número de entradas de datos y en las características eléctricas de la salida.

Algunos disponen de entrada de habilitación o enable (EN)

#### **Connection Diagrams**

#### 1.1. Multiplexor.

Existen diversos circuitos integrados multiplexores cuyas diferencias estriban, básicamente, en el número de entradas de datos y en las características eléctricas de la salida.

Algunos disponen de entrada de habilitación o enable (EN)

### 1.1. Multiplexor.

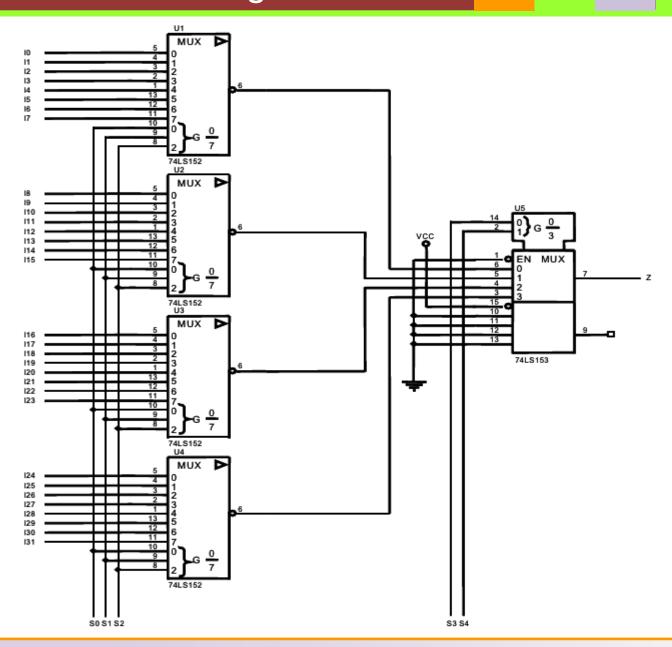

Se pueden construir multiplexores de mayor capacidad a partir de multiplexores con un número reducido de entradas.

Ejemplo: multiplexor de 32 entradas a partir de multiplexores de 8 entradas

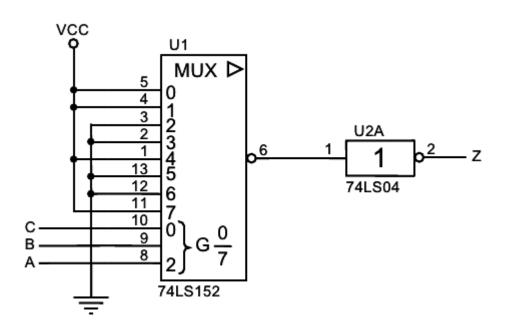

#### 1.1. Multiplexor.

Debido a su estructura lógica formada por dos niveles de puertas AND-OR, el multiplexor se puede utilizar para crear funciones lógicas

Función Lógica de n variables  $\Rightarrow$  multiplexor de n-1 o más entradas

$$Z = \overline{A} \cdot \overline{B} + A \cdot \overline{B} \cdot \overline{C} + A \cdot B \cdot C$$

| Α | В | С | Z |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

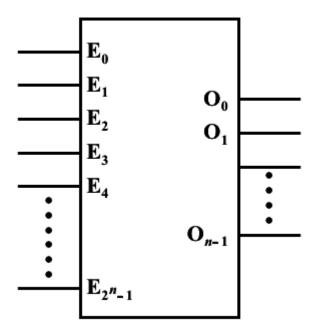

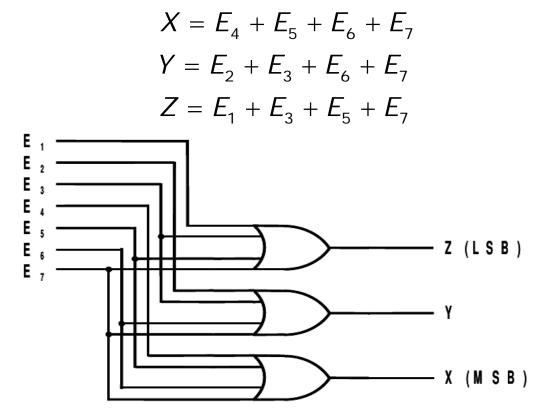

#### 1.2. Encoder.

Es un circuito combinacional lógico que acepta un máximo de 2<sup>n</sup> entradas de distintas características eléctricas (distintas fuentes) y genera n salidas (código binario) de tal forma que si hay una entrada activa, a la salida aparece la combinación binaria que representa a dicha entrada.

#### 1.2. Encoder.

| ENTRADAS       |   | SALIDAS |   |  |  |  |  |  |

|----------------|---|---------|---|--|--|--|--|--|

| E <sub>i</sub> | X | Y       | Z |  |  |  |  |  |

| $E_{o}$        | 0 | 0       | 0 |  |  |  |  |  |

| E <sub>1</sub> | 0 | 0       | 1 |  |  |  |  |  |

| $E_2$          | 0 | 1       | 0 |  |  |  |  |  |

| E <sub>3</sub> | 0 | 1       | 1 |  |  |  |  |  |

| E <sub>4</sub> | 1 | 0       | 0 |  |  |  |  |  |

| E <sub>5</sub> | 1 | 0       | 1 |  |  |  |  |  |

| E <sub>6</sub> | 1 | 1       | 0 |  |  |  |  |  |

| E <sub>7</sub> | 1 | 1       | 1 |  |  |  |  |  |

#### 1.2. Encoder.

#### CODIFICADOR DECIMAL A BINARIO NATURAL

| <b>I</b> <sub>7</sub> | <b>I</b> <sub>6</sub> | <b>I</b> <sub>5</sub> | <b>I</b> <sub>4</sub> | <b>I</b> <sub>3</sub> | l <sub>2</sub> | I <sub>1</sub> | I <sub>0</sub> | 02 | 01 | 00 |

|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------|----------------|----------------|----|----|----|

| 0                     | 0                     | 0                     | 0                     | 0                     | 0              | 0              | 1              | 0  | 0  | 0  |

| 0                     | 0                     | 0                     | 0                     | 0                     | 0              | 1              | 0              | 0  | 0  | 1  |

| 0                     | 0                     | 0                     | 0                     | 0                     | 1              | 0              | 0              | 0  | 1  | 0  |

| 0                     | 0                     | 0                     | 0                     | 1                     | 0              | 0              | 0              | 0  | 1  | 1  |

| 0                     | 0                     | 0                     | 1                     | 0                     | 0              | 0              | 0              | 1  | 0  | 0  |

| 0                     | 0                     | 1                     | 0                     | 0                     | 0              | 0              | 0              | 1  | 0  | 1  |

| 0                     | 1                     | 0                     | 0                     | 0                     | 0              | 0              | 0              | 1  | 1  | 0  |

| 1                     | 0                     | 0                     | 0                     | 0                     | 0              | 0              | 0              | 1  | 1  | 1  |

PROBLEMA: puede haber más de una entrada activa.

SOLUCIÓN: encoder de prioridad

#### 1.2. Encoder.

#### Encoder de prioridad

La salida responde a la entrada de mayor valor

| I <sub>7</sub> | I <sub>6</sub> | I <sub>5</sub> | I <sub>4</sub> | I <sub>3</sub> | I <sub>2</sub> | l <sub>1</sub> | I <sub>0</sub> | 02 | 01 | 00 |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|----|----|

| 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0  | 0  | 0  |

| 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0  | 0  | 0  |

| 0              | 0              | 0              | 0              | 0              | 0              | 1              | Χ              | 0  | 0  | 1  |

| 0              | 0              | 0              | 0              | 0              | 1              | Χ              | Χ              | 0  | 1  | 0  |

| 0              | 0              | 0              | 0              | 1              | Χ              | X              | Χ              | 0  | 1  | 1  |

| 0              | 0              | 0              | 1              | Χ              | Χ              | Χ              | Χ              | 1  | 0  | 0  |

| 0              | 0              | 1              | Χ              | Χ              | Χ              | X              | Χ              | 1  | 0  | 1  |

| 0              | 1              | X              | X              | X              | Χ              | X              | Χ              | 1  | 1  | 0  |

| 1              | Χ              | Χ              | Χ              | Χ              | Χ              | Χ              | Χ              | 1  | 1  | 1  |

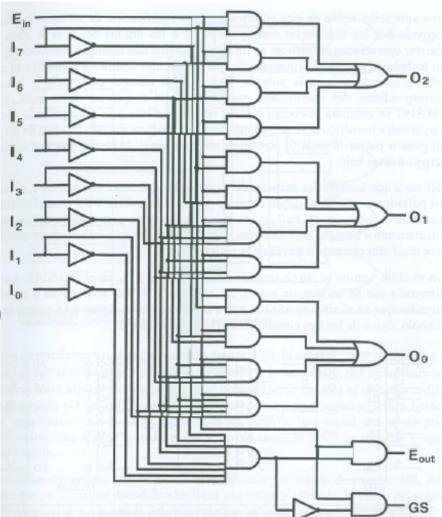

#### 1.2. Encoder.

#### Encoder de prioridad

| E <sub>in</sub> | I <sub>7</sub> | I <sub>6</sub> | I <sub>5</sub> | I <sub>4</sub> | I <sub>3</sub> | l <sub>2</sub> | l <sub>1</sub> | I <sub>0</sub> | 02 | 01 | 00 | GS | Eout |

|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|----|----|----|------|

| 0               | Χ              | Х              | Χ              | Χ              | Χ              | Χ              | Χ              | Χ              | 0  | 0  | 0  | 0  | 0    |

| 1               | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0  | 0  | 0  | 0  | 1    |

| 1               | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0  | 0  | 0  | 1  | 0    |

| 1               | 0              | 0              | 0              | 0              | 0              | 0              | 1              | Χ              | 0  | 0  | 1  | 1  | 0    |

| 1               | 0              | 0              | 0              | 0              | 0              | 1              | Χ              | Χ              | 0  | 1  | 0  | 1  | 0    |

| 1               | 0              | 0              | 0              | 0              | 1              | Χ              | Χ              | Χ              | 0  | 1  | 1  | 1  | 0    |

| 1               | 0              | 0              | 0              | 1              | Χ              | Χ              | Χ              | Χ              | 1  | 0  | 0  | 1  | 0    |

| 1               | 0              | 0              | 1              | Χ              | Χ              | Χ              | Χ              | Χ              | 1  | 0  | 1  | 1  | 0    |

| 1               | 0              | 1              | Χ              | Χ              | Χ              | X              | Χ              | Χ              | 1  | 1  | 0  | 1  | 0    |

| 1               | 1              | Χ              | Χ              | Χ              | X              | Χ              | X              | X              | 1  | 1  | 1  | 1  | 0    |

$$O_{2} = E_{in} (I_{4} + I_{5} + I_{6} + I_{7})$$

$$O_{1} = E_{in} (I_{2} \cdot \overline{I_{4}} \cdot \overline{I_{5}} + I_{3} \cdot \overline{I_{4}} \cdot \overline{I_{5}} + I_{6} + I_{7})$$

$$O_{0} = E_{in} (I_{1} \cdot \overline{I_{2}} \cdot \overline{I_{4}} \cdot \overline{I_{6}} + I_{3} \cdot \overline{I_{4}} \cdot \overline{I_{6}} + I_{5} \cdot \overline{I_{6}} + I_{7})$$

$$E_{out} = E_{in} \cdot \overline{I_{0}} \cdot \overline{I_{1}} \cdot \overline{I_{2}} \cdot \overline{I_{3}} \cdot \overline{I_{4}} \cdot \overline{I_{5}} \cdot \overline{I_{6}} \cdot \overline{I_{7}}$$

$$GS = E_{in} (I_{0} + I_{1} + I_{2} + I_{3} + I_{4} + I_{5} + I_{6} + I_{7})$$

#### 1.2. Encoder.

#### Encoder de prioridad

$$O_{2} = E_{in} (I_{4} + I_{5} + I_{6} + I_{7})$$

$$O_{1} = E_{in} (I_{2} \cdot \overline{I_{4}} \cdot \overline{I_{5}} + I_{3} \cdot \overline{I_{4}} \cdot \overline{I_{5}} + I_{6} + I_{7})$$

$$O_{0} = E_{in} (I_{1} \cdot \overline{I_{2}} \cdot \overline{I_{4}} \cdot \overline{I_{6}} + I_{3} \cdot \overline{I_{4}} \cdot \overline{I_{6}} + I_{5} \cdot \overline{I_{6}} + I_{7})$$

$$E_{out} = E_{in} \cdot \overline{I_{0}} \cdot \overline{I_{1}} \cdot \overline{I_{2}} \cdot \overline{I_{3}} \cdot \overline{I_{4}} \cdot \overline{I_{5}} \cdot \overline{I_{6}} \cdot \overline{I_{7}}$$

$$GS = E_{in} (I_{0} + I_{1} + I_{2} + I_{3} + I_{4} + I_{5} + I_{6} + I_{7})$$

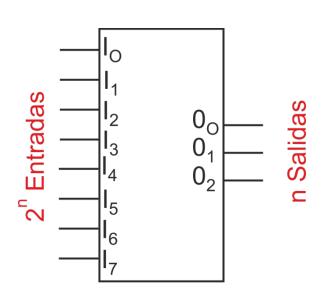

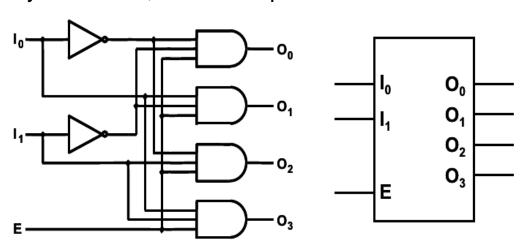

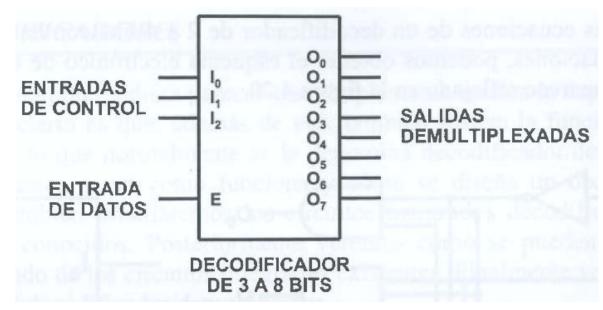

#### 1.3. Decodificador, demultiplexor.

Realiza la operación inversa al encoder: para cada combinación de entradas, sólo una de las salidas tiene un nivel lógico diferente a las demás (a la entrada se tiene una información codificada y a la salida se obtiene decodificada).

Los decodificadores tienen n entradas y m salidas, de forma que  $m \le 2^n$ .

| Е | I <sub>1</sub> | I <sub>0</sub> | O <sub>3</sub> | O <sub>2</sub> | O <sub>1</sub> | 00 |

|---|----------------|----------------|----------------|----------------|----------------|----|

| 1 | 0              | 0              | 0              | 0              | 0              | 1  |

| 1 | 0              | 1              | 0              | 0              | 1              | 0  |

| 1 | 1              | 0              | 0              | 1              | 0              | 0  |

| 1 | 1              | 1              | 1              | 0              | 0              | 0  |

| 0 | Χ              | Χ              | 0              | 0              | 0              | 0  |

$$O_0 = E \cdot \overline{I_0} \cdot \overline{I_1}$$

$O_1 = E \cdot I_0 \cdot \overline{I_1}$

$O_2 = E \cdot \overline{I_0} \cdot I_1$   $O_3 = E \cdot I_0 \cdot I_1$

#### 1.3. Decodificador, demultiplexor.

Demultiplexor: acción opuesta al multiplexor, tiene una única entrada cuyo valor se trasfiere a una de las múltiples salidas, seleccionada por medio de las entradas de control.

| S <sub>1</sub> | S <sub>0</sub> | O <sub>3</sub> | O <sub>2</sub> | 01 | <b>O</b> <sub>0</sub> |

|----------------|----------------|----------------|----------------|----|-----------------------|

| 0              | 0              | 0              | 0              | 0  | Е                     |

| 0              | 1              | 0              | 0              | Ε  | 0                     |

| 1              | 0              | 0              | Е              | 0  | 0                     |

| 1              | 1              | Е              | 0              | 0  | 0                     |

Demultiplexor de 1 a 4

Demultiplexor de 1 a 8

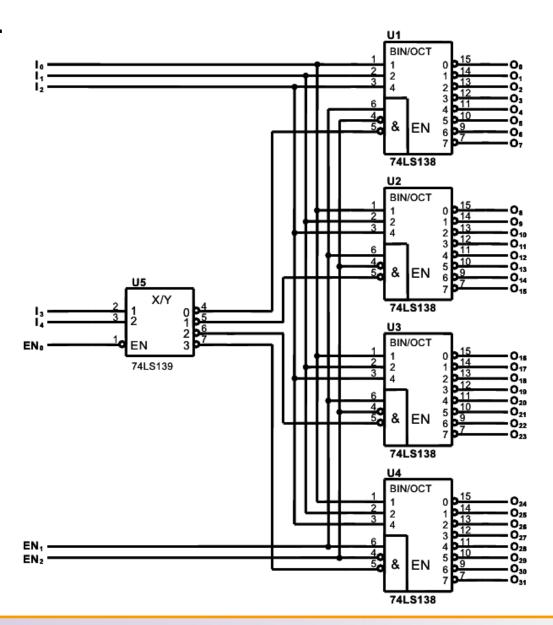

### 1.3. Decodificador, demultiplexor.

Mediante CI disponibles se puede aumentar la capacidad del decodificador/demultiplexor.

### 1.4. Convertidores de código.

Circuito combinacional que parte de un código de *N* bits y lo transforma en un código de *M* bits.

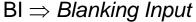

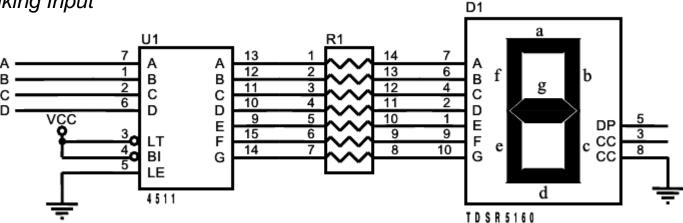

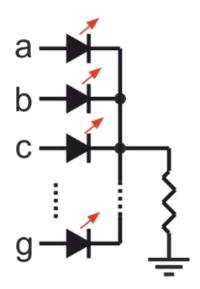

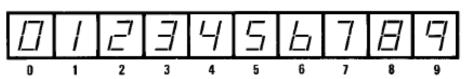

Ejemplo: conversor de código BCD a 7 segmentos.

Tabla de la verdad de un conversor de BCD a 7 segmentos

| N° | D | С | В | Α | а | b | С | d | е | f | g |

|----|---|---|---|---|---|---|---|---|---|---|---|

| 0  | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1  | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2  | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3  | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4  | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5  | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6  | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7  | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8  | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9  | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

LT ⇒ Test Lamp

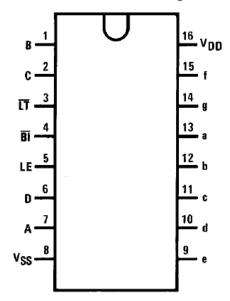

### 1.4. Convertidores de código.

### 1.4. Convertidores de código.

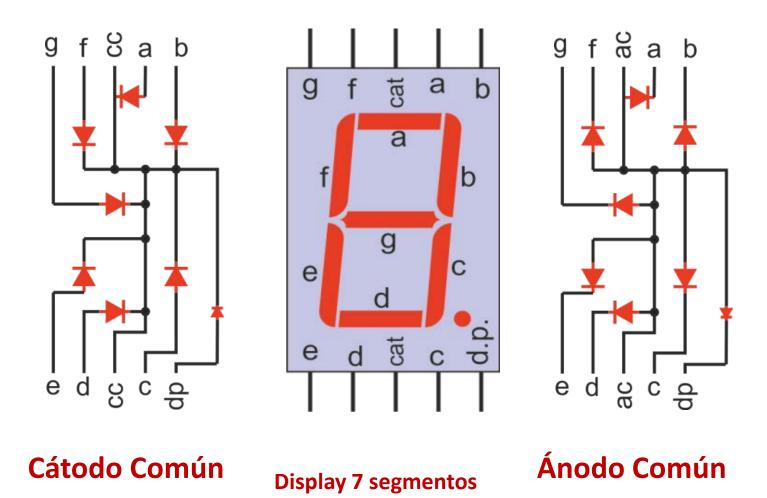

Es imprescindible poner resistencias para limitar la corriente por los diodos

Todos los diodos lucen con igual intensidad siempre

Los diodos lucen con distinta intensidad, dependiendo de cuantos estén en ON

### 1.4. Convertidores de código.

#### **Connection Diagram**

**Dual-In-Line Package**

CD4511

#### Segment Identification

#### **Truth Table**

|    |    | Inp | uts |   |   |   |   |   |   | ( | Out | put | s |         |

|----|----|-----|-----|---|---|---|---|---|---|---|-----|-----|---|---------|

| LE | BI | LT  | D   | С | В | Α | а | b | С | d | е   | f   | g | Display |

| X  | X  | 0   | Х   | Χ | Χ | Χ | 1 | 1 | 1 | 1 | 1   | 1   | 1 | В       |

| X  | 0  | 1   | Х   | X | Х | X | 0 | 0 | 0 | 0 | 0   | 0   | 0 |         |

| 0  | 1  | 1   | 0   | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1   | 1   | 0 | 0       |

| 0  | 1  | 1   | 0   | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0   | 0   | 0 | 1       |

| 0  | 1  | 1   | 0   | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1   | 0   | 1 | 2       |

| 0  | 1  | 1   | 0   | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0   | 0   | 1 | 3       |

| 0  | 1  | 1   | 0   | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0   | 1   | 1 | 4       |

| 0  | 1  | 1   | 0   | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0   | 1   | 1 | 5       |

| 0  | 1  | 1   | 0   | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1   | 1   | 1 | 6       |

| 0  | 1  | 1   | 0   | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0   | 0   | 0 | 7       |

| 0  | 1  | 1   | 1   | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1   | 1   | 1 | 8       |

| 0  | 1  | 1   | 1   | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0   | 1   | 1 | 9       |

| 0  | 1  | 1   | 1   | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0   | 0   | 0 |         |

| 0  | 1  | 1   | 1   | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0   | 0   | 0 |         |

| 0  | 1  | 1   | 1   | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0   | 0   | 0 |         |

| 0  | 1  | 1   | 1   | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0   | 0   | 0 |         |

| 0  | 1  | 1   | 1   | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0   | 0   | 0 |         |

| 0  | 1  | 1   | 1   | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0   | 0   | 0 |         |

| 1  | 1  | 1   | Х   | Χ | X | Χ |   |   |   | * |     |     |   | *       |

X = Don't Care

#### Display

<sup>\*</sup>Depends upon the BCD code applied during the 0 to 1 transition of LE.

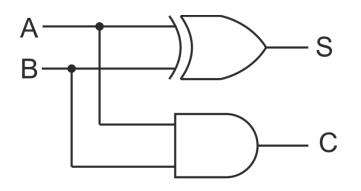

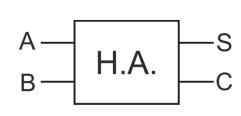

#### 2.1. Sumador binario.

### **Semisumador (Half-Adder)**

Circuito que realiza la suma de dos bits sin tener en cuenta la llevada

| Α | В | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

$$S = A \oplus B$$

$$C = A \cdot B$$

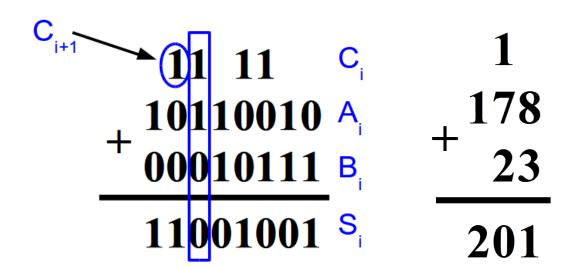

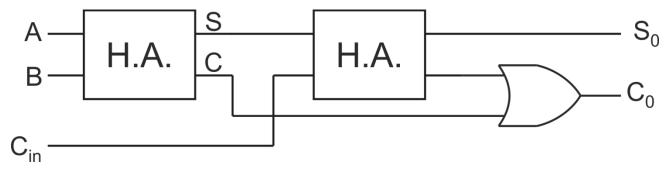

#### 2.1. Sumador binario.

Sumador completo (Full-Adder)

Circuito que realiza la suma de dos bits teniendo en cuenta las llevadas

#### 2.1. Sumador binario.

#### **Sumador completo (Full-Adder)**

| Α | В | C <sub>in</sub> | S <sub>0</sub> | C <sub>0</sub> |

|---|---|-----------------|----------------|----------------|

| 0 | 0 | 0               | 0              | 0              |

| 0 | 1 | 0               | 1              | 0              |

| 1 | 0 | 0               | 1              | 0              |

| 1 | 1 | 0               | 0              | 1              |

| 0 | 0 | 1               | 1              | 0              |

| 0 | 1 | 1               | 0              | 1              |

| 1 | 0 | 1               | 0              | 1              |

| 1 | 1 | 1               | 1              | 1              |

$$S_{i} = \overline{A}_{i} \cdot B_{i} \cdot \overline{C}_{i} + A_{i} \cdot \overline{B}_{i} \cdot \overline{C}_{i} + \overline{A}_{i} \cdot \overline{B}_{i} \cdot C_{i} + A_{i} \cdot B_{i} \cdot C_{i} =$$

$$= (\overline{A}_{i} \cdot B_{i} + A_{i} \cdot \overline{B}_{i}) \cdot \overline{C}_{i} + (\overline{A}_{i} \cdot \overline{B}_{i} + A_{i} \cdot B_{i}) \cdot C_{i} =$$

$$= A_{i} \oplus B_{i} \cdot \overline{C}_{i} + \overline{A_{i} \oplus B_{i}} \cdot C_{i} =$$

$$= A_{i} \oplus B_{i} \oplus C_{i}$$

$$C_{i+1} = A_{i} \cdot B_{i} + A_{i} \cdot C_{i} + B_{i} \cdot C_{i}$$

$$F.A.$$

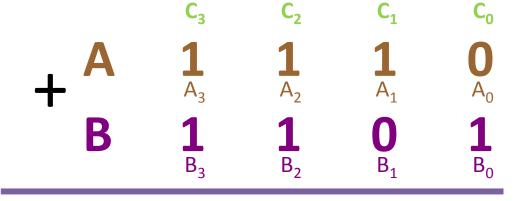

#### 2.1. Sumador binario.

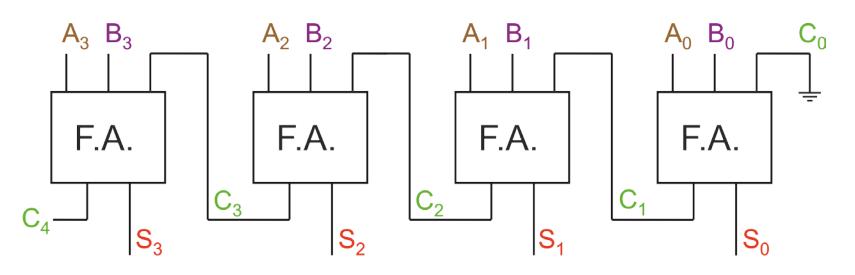

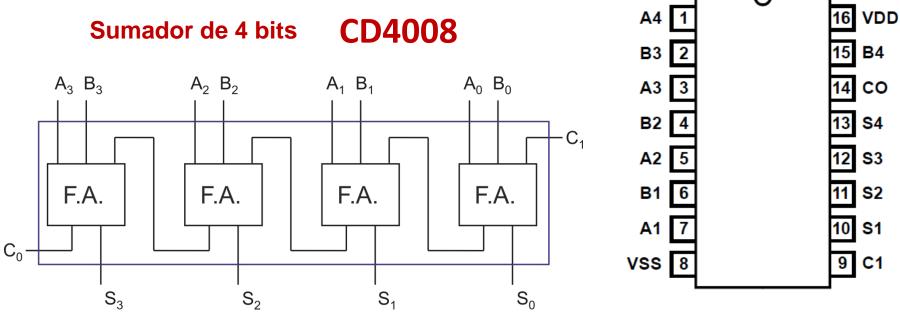

Sumador de 4 bits

#### 2.1. Sumador binario.

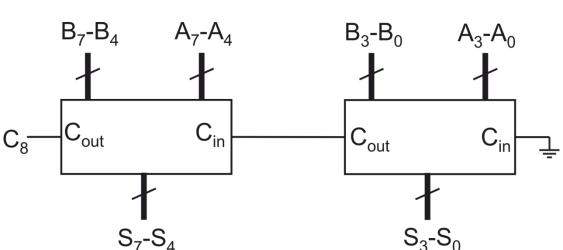

Se pueden acoplar en cascada para sumar números de más bits

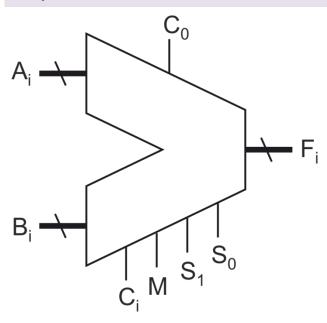

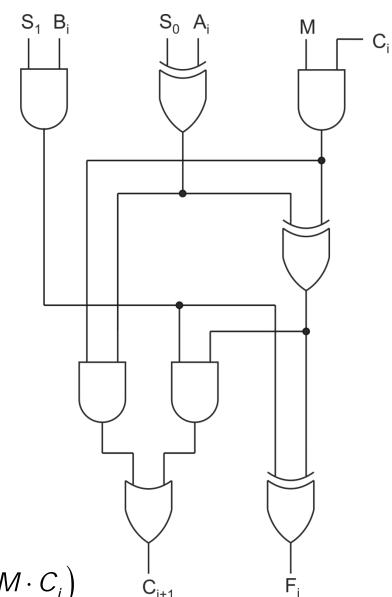

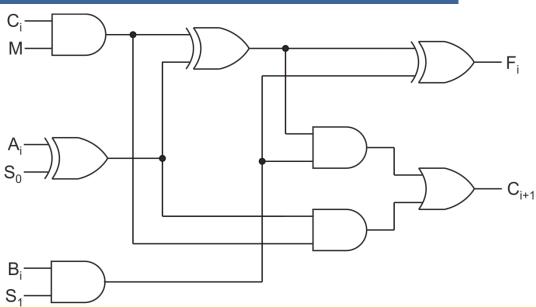

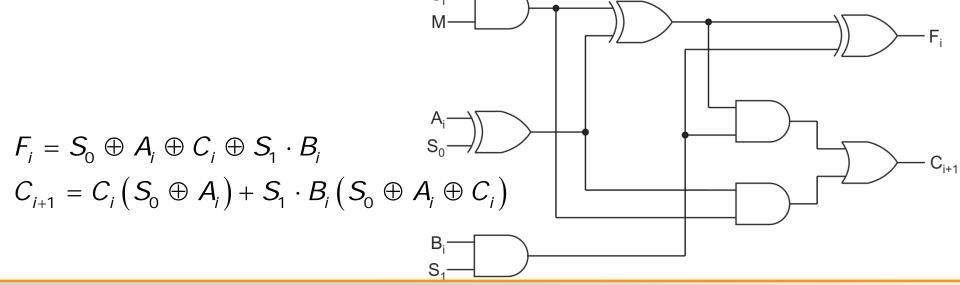

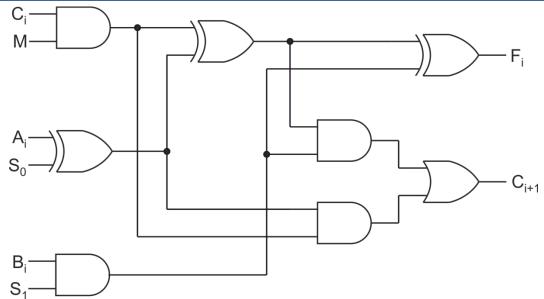

### 2.2. Unidad Lógica Aritmética (ALU).

#### **Arithmetic Logic Unit**

Circuito combinacional que realiza operaciones aritméticas y/o lógicas dependiendo de unas variables de control

$$F_{i} = ((S_{0} \oplus A_{i}) \oplus M \cdot C_{i}) \oplus S_{1} \cdot B_{i}$$

$$C_{i+1} = M \cdot C_i \left( S_0 \oplus A_i \right) + S_1 \cdot B_i \left( \left( S_0 \oplus A_i \right) \oplus M \cdot C_i \right)$$

### 2.2. Unidad Lógica Aritmética (ALU).

| M=0 (Función Lógica) |                |                                   |                                       |  |  |

|----------------------|----------------|-----------------------------------|---------------------------------------|--|--|

| S <sub>1</sub>       | S <sub>0</sub> | F <sub>i</sub> (F. Lógica)        | Comentario                            |  |  |

| 0                    | 0              | $F_i = A_i$                       | Entrada A transferida a la salida     |  |  |

| 0                    | 1              | $F_i = \overline{A}_i$            | Entrada A complementada y transferida |  |  |

| 1                    | 0              | $F_i = A_i \oplus B_i$            | XOR                                   |  |  |

| 1                    | 1              | $F_i = \overline{A_i \oplus B_i}$ | XNOR                                  |  |  |

$$F_{i} = S_{0} \oplus A_{i} \oplus S_{1} \cdot B_{i}$$

$$C_{i+1} = S_{1} \cdot B_{i} (S_{0} \oplus A_{i})$$

### 2.2. Unidad Lógica Aritmética (ALU).

| M=1 (Función Aritmética) y C <sub>i</sub> = 0 |       |                                |                                       |  |  |

|-----------------------------------------------|-------|--------------------------------|---------------------------------------|--|--|

| $S_1$                                         | $S_0$ | F <sub>i</sub> (F. aritmética) | Comentario                            |  |  |

| 0                                             | 0     | $F_i = A_i$                    | Entrada A transferida a la salida     |  |  |

| 0                                             | 1     | $F_i = \overline{A}_i$         | Complemento a uno de A                |  |  |

| 1                                             | 0     | $F_i = A_i + B_i$              | Suma de A y B                         |  |  |

| 1                                             | 1     | $F_i = \overline{A_i} + B_i$   | Suma de B y el complemento a uno de A |  |  |

### 2.2. Unidad Lógica Aritmética (ALU).

| M=1 (Función Aritmética) y C <sub>i</sub> = 1 |       |                                  |                             |  |  |

|-----------------------------------------------|-------|----------------------------------|-----------------------------|--|--|

| S <sub>1</sub>                                | $S_0$ | F <sub>i</sub> (F. aritmética)   | Comentario                  |  |  |

| 0                                             | 0     | $F_i = A_i + 1$                  | Incrementa A                |  |  |

| 0                                             | 1     | $F_i = \overline{A}_i + 1$       | Complemento a dos de A      |  |  |

| 1                                             | 0     | $F_i = A_i + B_i + 1$            | Incrementa la suma de A y B |  |  |

| 1                                             | 1     | $F_i = \overline{A_i} + B_i + 1$ | B menos A                   |  |  |

### 2.2. Unidad Lógica Aritmética (ALU).

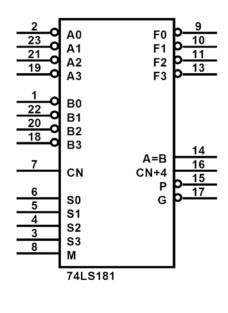

La ALU 4-bit 74LS181

### **Pin Descriptions**

| Pin Names        | Description                         |  |  |

|------------------|-------------------------------------|--|--|

| Ā0-Ā3            | Operand Inputs (Active LOW)         |  |  |

| B0−B3            | Operand Inputs (Active LOW)         |  |  |

| S0-S3            | Function Select Inputs              |  |  |

| М                | Mode Control Input                  |  |  |

| C <sub>n</sub>   | Carry Input                         |  |  |

| F0-F3            | Function Outputs (Active LOW)       |  |  |

| A = B            | Comparator Output                   |  |  |

| Ğ                | Carry Generate Output (Active LOW)  |  |  |

| P                | Carry Propagate Output (Active LOW) |  |  |

| C <sub>n+4</sub> | Carry Output                        |  |  |

### 2.2. Unidad Lógica Aritmética (ALU).

La ALU 4-bit 74LS181

#### **Function Table**

| Mode Select |    |    |    | Active LOW Operands                |                                                      | Active HIGH Operands               |                                                      |

|-------------|----|----|----|------------------------------------|------------------------------------------------------|------------------------------------|------------------------------------------------------|

| Inputs      |    |    |    | & F <sub>n</sub> Outputs           |                                                      | & F <sub>n</sub> Outputs           |                                                      |

|             |    |    |    | Logic                              | Arithmetic<br>(Note 2)                               | Logic                              | Arithmetic<br>(Note 2)                               |

| S3          | S2 | S1 | S0 | (M = H)                            | $(\mathbf{M}=\mathbf{L})\;(\mathbf{C_n}=\mathbf{L})$ | (M = H)                            | $(\mathbf{M}=\mathbf{L})\;(\mathbf{C_n}=\mathbf{H})$ |

| L           | L  | L  | L  | Ā                                  | A minus 1                                            | Ā                                  | A                                                    |

| L           | L  | L  | Н  | ĀB                                 | AB minus 1                                           | $\overline{A} + \overline{B}$      | A + B                                                |

| L           | L  | Н  | L  | $\overline{A} + \overline{B}$      | AB minus 1                                           | ĀВ                                 | $A + \overline{B}$                                   |

| L           | L  | Н  | Н  | Logic 1                            | minus 1                                              | Logic 0                            | minus 1                                              |

| L           | Н  | L  | L  | $\overline{A} + \overline{B}$      | A plus $(A + \overline{B})$                          | ĀB                                 | A plus AB                                            |

| L           | Н  | L  | Н  | B                                  | AB plus $(A + \overline{B})$                         | B                                  | $(A + B)$ plus $A\overline{B}$                       |

| L           | Н  | Н  | L  | $\overline{A} \oplus \overline{B}$ | A minus B minus 1                                    | A ⊕ B                              | A minus B minus 1                                    |

| L           | Н  | Н  | Н  | A + B                              | $A + \overline{B}$                                   | ΑB                                 | AB minus 1                                           |

| Н           | L  | L  | L  | ĀB                                 | A plus (A + B)                                       | Ā + B                              | A plus AB                                            |

| Н           | L  | L  | Н  | A⊕B                                | A plus B                                             | $\overline{A} \oplus \overline{B}$ | A plus B                                             |

| Н           | L  | Н  | L  | В                                  | $A\overline{B}$ plus $(A + B)$                       | В                                  | $(A + \overline{B})$ plus AB                         |

| Н           | L  | Н  | Н  | A + B                              | A + B                                                | AB                                 | AB minus 1                                           |

| - H         | Н  | L  | L  | Logic 0                            | A plus A (Note 1)                                    | Logic 1                            | A plus A (Note 1)                                    |

| Н           | Н  | L  | Н  | ΑB                                 | AB plus A                                            | A + B                              | (A + B) plus A                                       |

| Н           | Н  | Н  | L  | AB                                 | AB minus A                                           | A + B                              | $(A + \overline{B})$ plus A                          |

| Н           | Н  | Н  | Н  | А                                  | Α                                                    | А                                  | A minus 1                                            |

Note 1: Each bit is shifted to the next most significant position.

Note 2: Arithmetic operations expressed in 2s complement notation.

#### Problemas.

1.- Resolver el problema de controlar una lámpara con 3 interruptores de manera que al variar uno de ellos la lámpara varíe. a) Utilizar puertas lógicas, b) multiplexor de 8:1, c) multiplexor de 4:1, d) decodificador de 3 entradas.

- 2.- Un proceso tiene 3 indicadores de temperatura del punto p cuyas salidas T1, T2 y T3 adoptan dos niveles de tensión bien diferenciadas, según que la temperatura sea menor o mayor e igual que t1, t2, t3 respectivamente, t1 < t2 < t3 ( temp < t  $\rightarrow$  T = 0, y si temp  $\geq$  t  $\rightarrow$  T = 1). Se desea generar una señal que adopte un nivel 1 lógico si la temperatura está comprendida entre t1 y t2, o es igual o superior a t3, y nivel 0 lógico en caso contrario.

- 2.1.- Realizar el circuito eléctrico con puertas lógicas.

- 2.2.- Realizar el circuito eléctrico con un decodificador de 4 entradas

- 2.3.- Realizar el circuito eléctrico con un multiplexor de 4 a 1.

- 3.- Realizar un circuito combinacional que realice la suma aritmética de dos números binarios, uno de un bit, y otro de dos bits, y cuyo resultado también esté dado en binario. Representar el circuito mediante puertas lógicas.

#### Problemas.

- 4.- Realizar un multiplexor de 4 entradas de datos en función de multiplexores de 2 entradas de datos.

- 5.- Realizar un decodificador de 4 entradas y 16 salidas a partir de decodificadores de 2 entradas y 4 salidas

- 6.- Diseñar un codificador que convierta una información en binario natural de 3 bits en un código de 7 segmentos (utilizar un display de 7 segmentos de cátodo común como el mostrado en la diapositiva 21)